Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Select Language

The design of all chips, like common products, requires a standardized flow of standards. The engineers then follow the flow, run and debug the parameters to get a qualified result.

With the continuous development of EDA software, new technologies continue to emerge, and flow selectivity also presents a diversified trend. Therefore, understanding new knowledge and new technologies are very necessary for us.

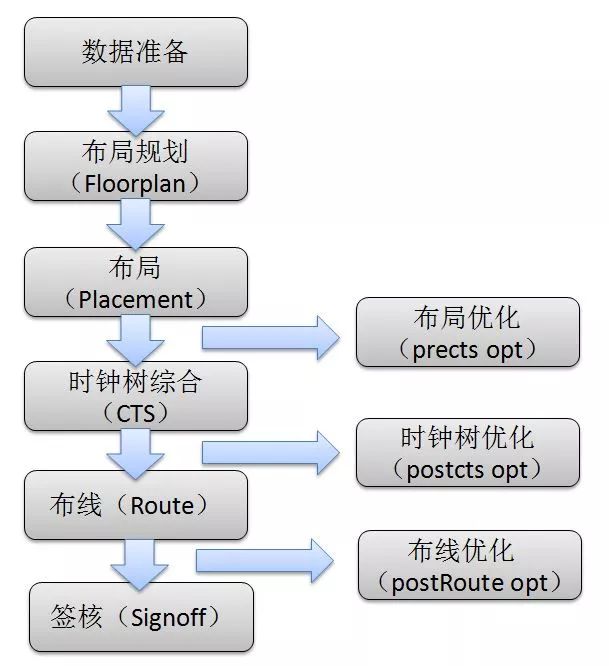

From the general direction of design, flow is divided into traditional flat flow and hierarchical flow. The flat design is the most basic method in integrated circuit design. The chip is optimized in the global scope, physical design is realized through layout winding, RC parameters are extracted for timing analysis, and finally the GDSII document is generated to complete the whole process. Simply refer to the following flat flow diagram:

Flattened designs usually yield better timing results, but they require an extremely long design cycle. With the rapid development of electronic technology, the number of logic cells on a single chip has increased from tens of thousands to tens of millions or even hundreds of millions of gates. This is a great challenge for EDA tools, engineers, and even computer hardware. At this time, a hierarchical flow scheme (Hier flow) was created.

Hierarchical design means that for an ordinary design, a hierarchical device (hinst) is logically defined, a physical constraint is physically given to the hierarchical device, and then a hierarchical device with physical constraints is defined as a partition. (Partition), and then cut out the entire design of the entire design, the remaining part is saved as a top-level design (top), and the individual partitions are saved separately, for the top-level, the cut-out partition is treated as a black box, For a single partition, it is considered chip level design when doing block implementation. After completing the block implementation and the top implementation, the partitions are finally assemble together to complete the full chip sign off. The simple diagram is as follows:

The greatest advantage of the hierarchical design scheme is that it will be a large design into multiple small designs. If there are timing problems that may exist in individual modules and then focus on solutions, the complexity becomes smaller and it is local. At the same time, the workload shared by each engineer is also smaller, and the cycle of completing the design will be shortened, thereby accelerating the design convergence.

Of course, there are many unavoidable deficiencies in hierarchical design, the most prominent being the errors arising from timing estimation. This error tends to make timing difficult to converge when doing the physical implementation of the partition. Or even though the partition satisfies the timing convergence condition, after the full-chip merging, some timing paths will become extremely poor. In situations where manual ECOs are not valid, this situation may require re-doing the physical implementation of the timing estimation and partitioning, which in the worst case may lead to the risk of re-adjusting the layout plan. In order to solve these problems, the traditional hierarchical design method also proposes many more advanced design concepts to improve the timing accuracy. These methods are applied in various steps in the hierarchical design. From the standpoint of timing convergence, flattening design is much more accurate than hierarchical design. Therefore, when the scale of the design does not reach the flat design method, the designer will prefer to use the flat design method.

Письмо этому поставщику

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.